1.软件版本

vivado2019.2,matlab2022a

2.运行方法

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。视频播放使用windows media player播放。

使用matlab2022a或者高版本仿真,运行文件夹中的tops.m或者main.m。运行时注意matlab左侧的当前文件夹窗口必须是当前工程所在路径。具体操作观看提供的程序操作视频跟着操作。视频播放使用windows media player播放。

3.部分仿真截图

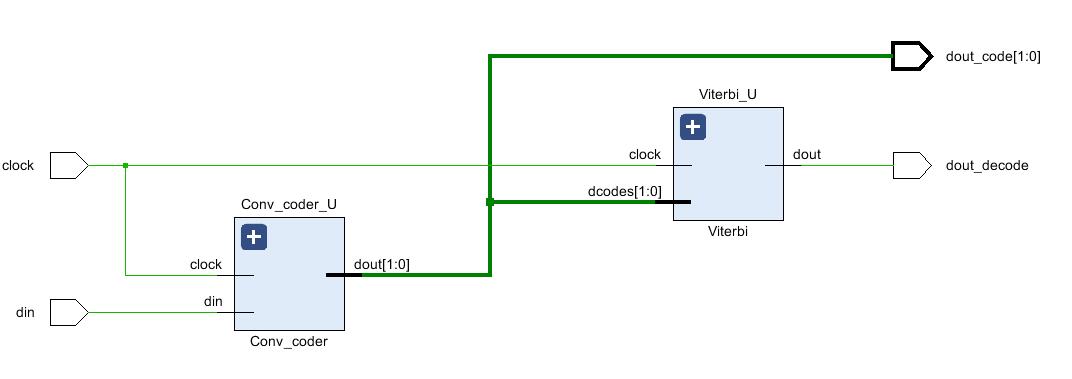

RTL图

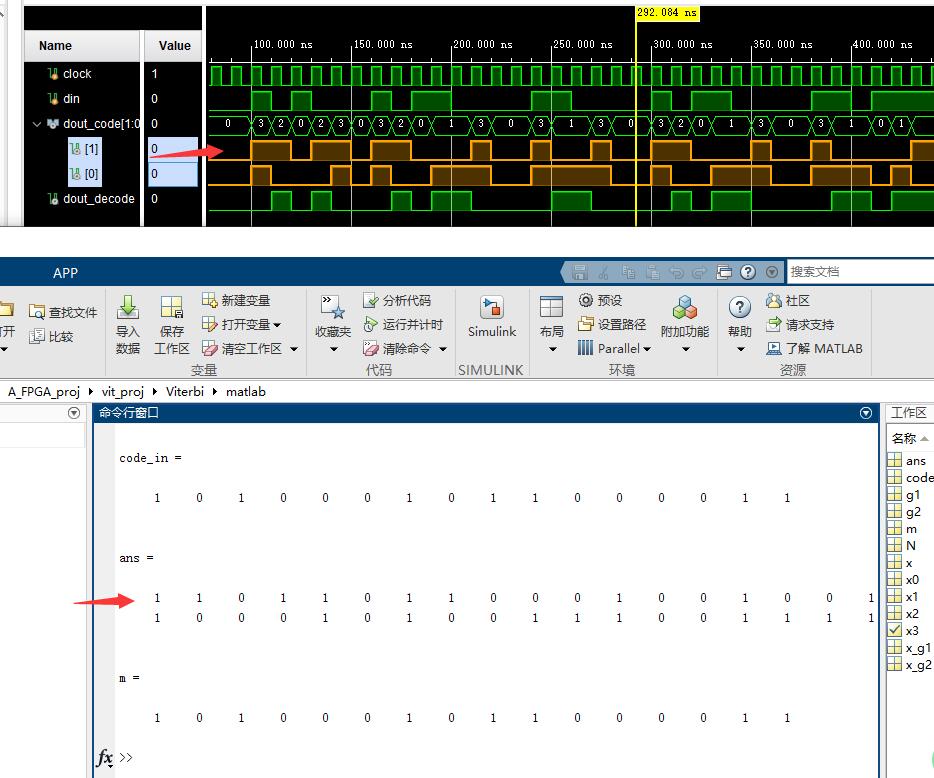

仿真图

和matlab对比图

可以看到编码,译码数据和matlab仿真结果完全对应

4.内容简介

卷积码是一个有限记忆系统,它也将信息序列分割成长度k的一个个分组,然后将k个信息比特编成n个比特,但k和n通常很小,特别适合以串行形式进行传输,时延小。与分组码不同的是在某一分组编码时,不仅参看本时刻的分组而且参看以前的N-1个分组,编码过程中互相关联的码元个数为nN。N称为约束长度。常把卷积码写成(n,k,N-1)卷积码。正因为卷积码在编码过程中,充分利用了各级之间的相关性,无论是从理论上还是实际上均已证明其性能要优于分组码。