1.软件版本

vivado2019.2

2.运行方法

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。视频播放使用windows media player播放。

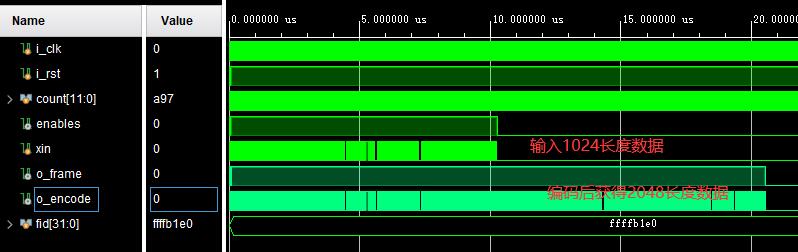

3.部分仿真截图

4.内容简介

CCSDS标准定义了一套适用于空间通信系统的LDPC编码方案,该方案规定了特定的校验矩阵结构和编码流程。对于CCSDS-LDPC(1024,512)码,其特点是使用准循环结构,确保了良好的纠错性能和较低的实现复杂度。在实际编码过程中,CCSDS LDPC编码器通常采用一种高效的硬件友好的编码算法,例如累积和编码(Accumulate-Repeat-Jagged-Edge,ARJ)或其他适合于准循环结构的算法。若已知CCSDS-LDPC(1024,512)码的校验矩阵H,编码过程可以简化为:

1).将信息比特序列按照指定方式填充到一个长度为1024的向量u中;

2).对于每一个校验节点对应的子矩阵块,计算其线性组合,如果结果不符合偶校验条件,则相应地翻转变量节点比特,直至满足所有校验关系。