包括程序操作录像

需要quartusii版本的朋友可以搜索本店铺同名资源

1.软件版本

vivado2019.2

2.运行方法

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。视频播放使用windows media player播放。

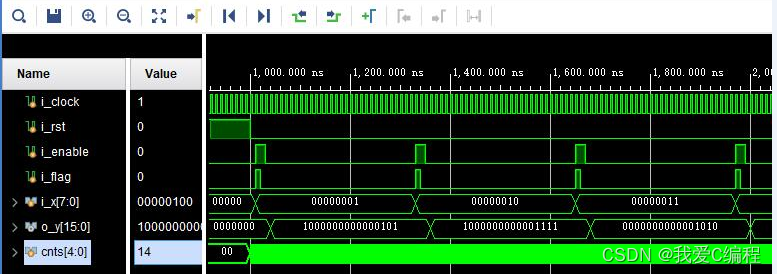

3.部分仿真截图

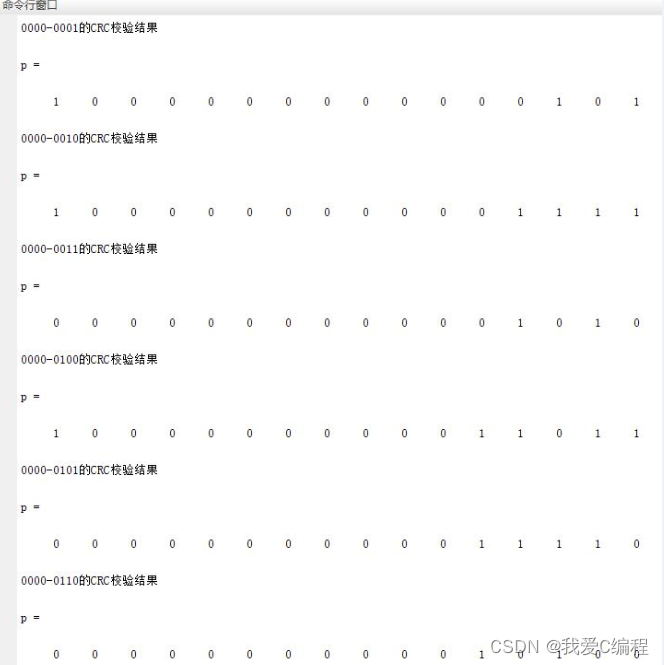

对比matlab结果:

4.内容简介

CRC(Cyclic Redundancy Check)是一种广泛应用于通信和存储系统中的数据校验技术。它通过对数据进行多项式除法操作来生成冗余校验码,并将其附加到数据中发送到接收方,接收方在接收到数据后再次进行多项式除法计算,如果计算得到的校验码与接收到的校验码相同,则表明数据没有发生错误。

CRC校验的基本原理是通过对数据进行多项式除法操作来生成冗余校验码。具体来说,假设要对一个N位的数据进行CRC校验,生成一个M位的校验码,其中M通常比N小,一般取16位或32位。生成多项式一般表示为G(x),它是一个M+1位的二进制数,最高位和最低位均为1。生成多项式的选择对于CRC校验的性能至关重要。