如果需要quartusii版本的朋友可以搜索本店铺同名资源

包括程序操作录像

1.软件版本

vivado2019.2

2.运行方法

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。视频播放使用windows media player播放。

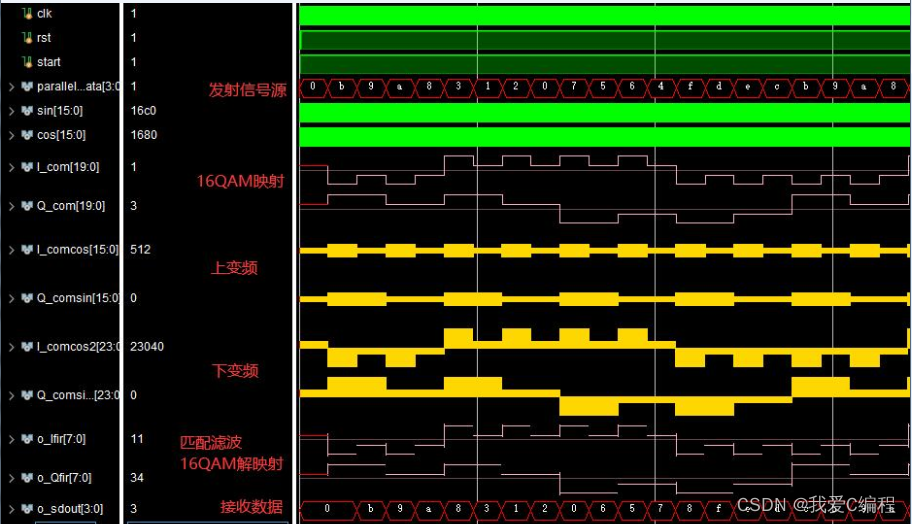

3.部分仿真截图

4.内容简介

数字信号是通过FPGA的输出端口生成的。在16QAM调制中,每个符号包含4个比特,因此需要一个4位二进制计数器来生成数字信号。计数器的输出被映射到星座图上的一个点,然后通过数字到模拟转换器(DAC)转换为模拟信号。串/并变换器将速率为Rb的二进制码元序列分为两路,速率为Rb/2.2-4电平变换为Rb/2 的二进制码元序列变成速率为RS=Rb/log216 的 4 个电平信号,4 电平信号与正交载波相乘,完成正交调制,两路信号叠加后产生 16QAM信号.在两路速率为Rb/2 的二进制码元序列中,经 2-4 电平变换器输出为 4 电平信号,即M=16.经 4 电平正交幅度调制和叠加后,输出 16 个信号状态,即 16QAM.