包括程序操作录像+说明文档+参考文献

1.软件版本

matlab2022a,vivado2019.2

2.运行方法

使用matlab2022a或者高版本仿真,运行文件夹中的tops.m或者main.m。运行时注意matlab左侧的当前文件夹窗口必须是当前工程所在路径。

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。视频播放使用windows media player播放。

3.部分仿真截图

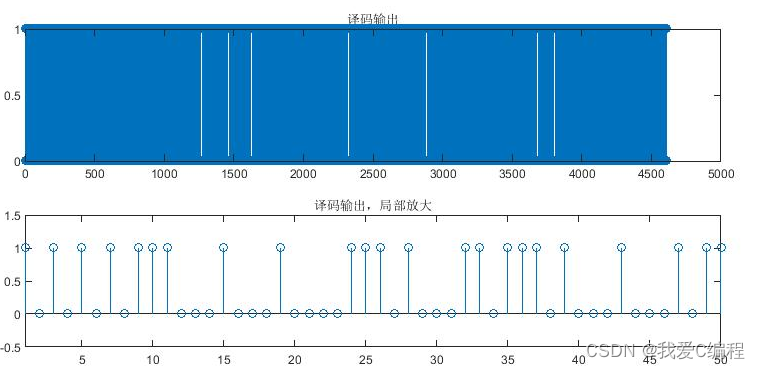

0.5码率,H是4608×9216的矩阵。

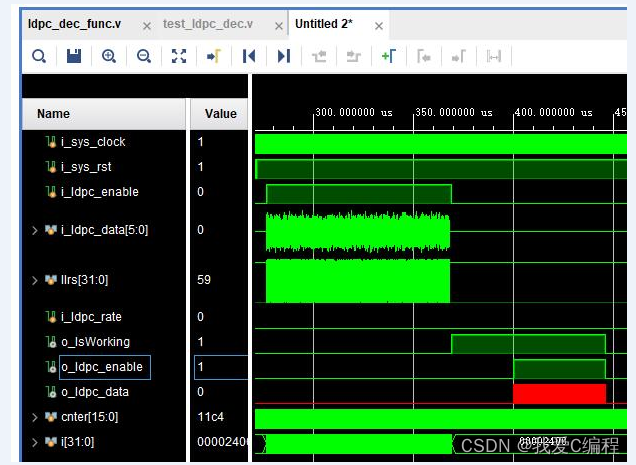

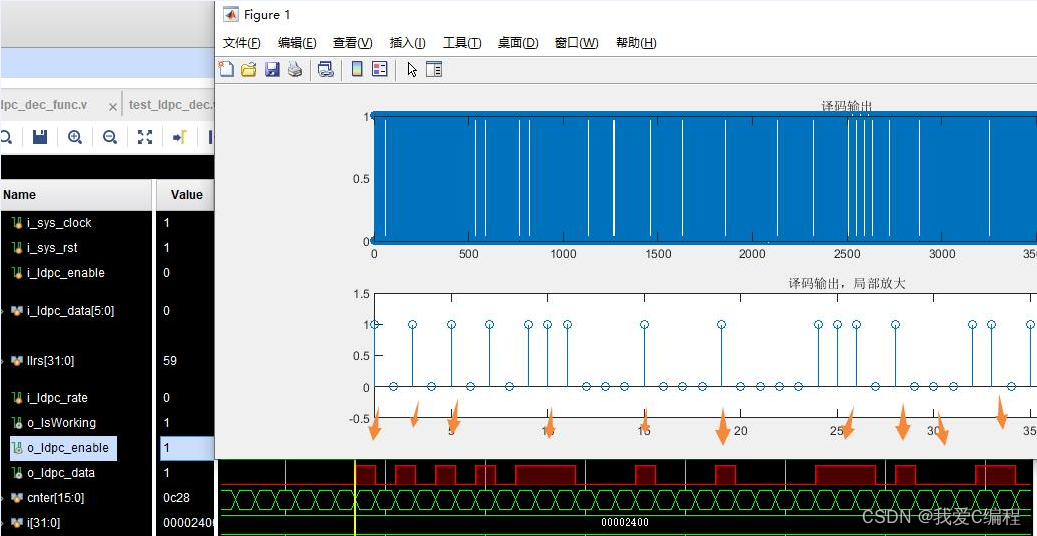

FPGA仿真:

对比如下:

4.内容简介

其中最小和算法的译码过程如下所示:

基于最小和算法的译码器设计的基本思想是:根据密度进化理论优化量化译码器参数,使量化译码器能达到最高的阈值。

整个算法的流程按如下步骤进行:

第一:初始化各个变量节点的值,赋初值;

第二:判断迭代次数是否已经超过了预设的最大迭代次数,如果超过,则迭代结束;

第三:每次迭代,变量节点的信息进行更新;

第四:计算每个变量节点Vn上的L值

第五:对每个变量节点Vn,对L值进行判决,输出序列Vk,从而结束译码;