1.软件版本

vivado2019.2

2.运行方法

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。视频播放使用windows media player播放。

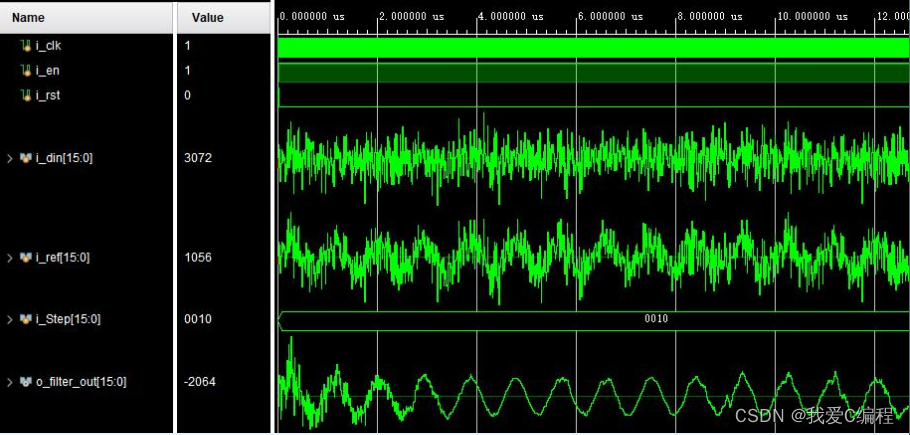

3.部分仿真截图

4.内容简介

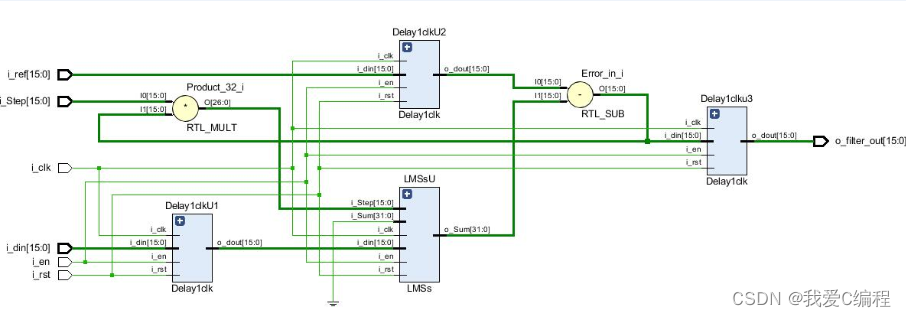

自适应算法用于估算随时间变化的信号。有许多自适应算法,如递归最小二乘(RLS)和卡尔曼滤波,但最常用的是最小均方算法(LMS)。这是一个简单但功能强大的算法,该算法可以利用莱迪思FPGA架构来实现。通过窗口和Hoff的开发,该算法采用的是梯度下降法来估计随时间变化的信号。梯度下降法找到一个最小值,如果它存在,在梯度负方向采取步骤。这样做是通过调整滤波器系数使误差最小化。

LMS参考设计包括两个主要的功能模块 - 一个FIR滤波器和LMS算法。使用一个乘法器和一个具有反馈的加法器串行实现FIR滤波器。 FIR结果归一化,以尽量减少饱和。 LMS算法迭代更新系数,并把其馈送到FIR滤波器。FIR滤波器使用系数c(n)和输入的参考信号x(n)生成输出y(n)。然后所希望的信号d(n)与输出y(n)相减,产生一个误差,LMS算法用它来计算下一组的系数。