1.软件版本

vivado2019.2

2.运行方法

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。视频播放使用windows media player播放。

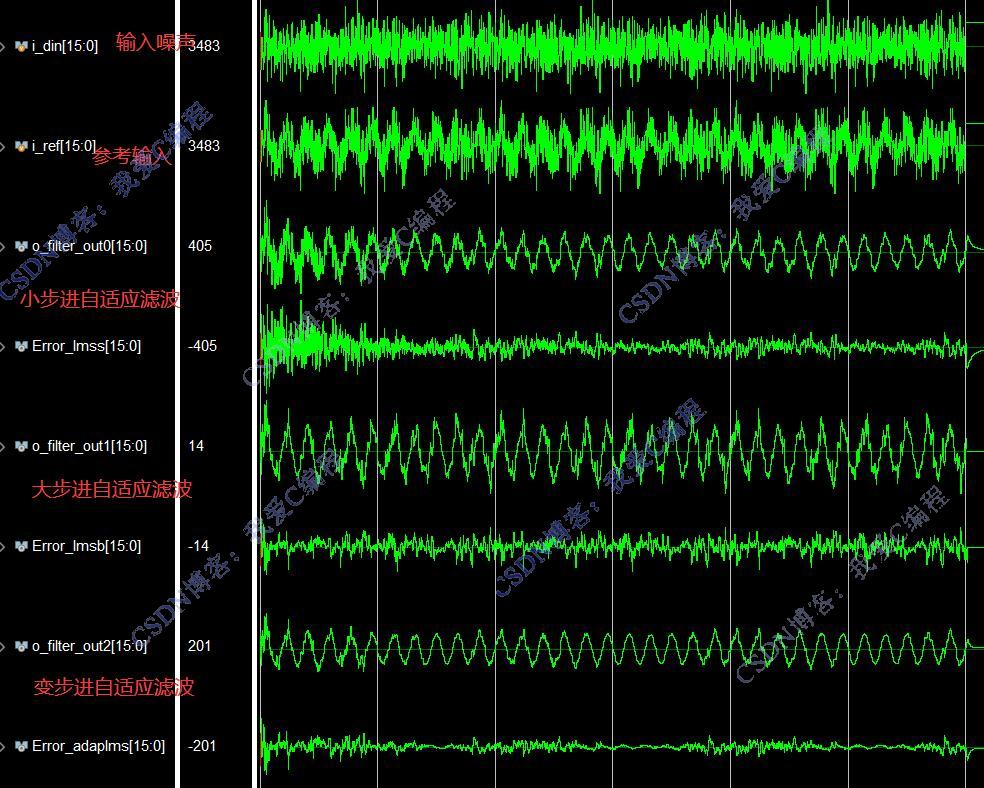

3.部分仿真截图

4.内容简介

自适应滤波器在信号处理领域有着广泛的应用,如通信中的信道均衡、噪声消除、系统辨识等。最小均方(Least Mean Square,LMS)算法是一种经典的自适应滤波算法,因其简单易实现而备受关注。基于现场可编程门阵列(Field Programmable Gate Array,FPGA)实现变步长 LMS 自适应滤波器,可以充分利用 FPGA 的并行处理能力和可重构性,提高滤波器的性能和灵活性。