付费后,使用电脑网页打开作品链接,点击弹出下载按键进行下载,包括程序操作录像

1.软件版本

vivado2019.2

2.运行方法

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。视频播放使用windows media player播放。

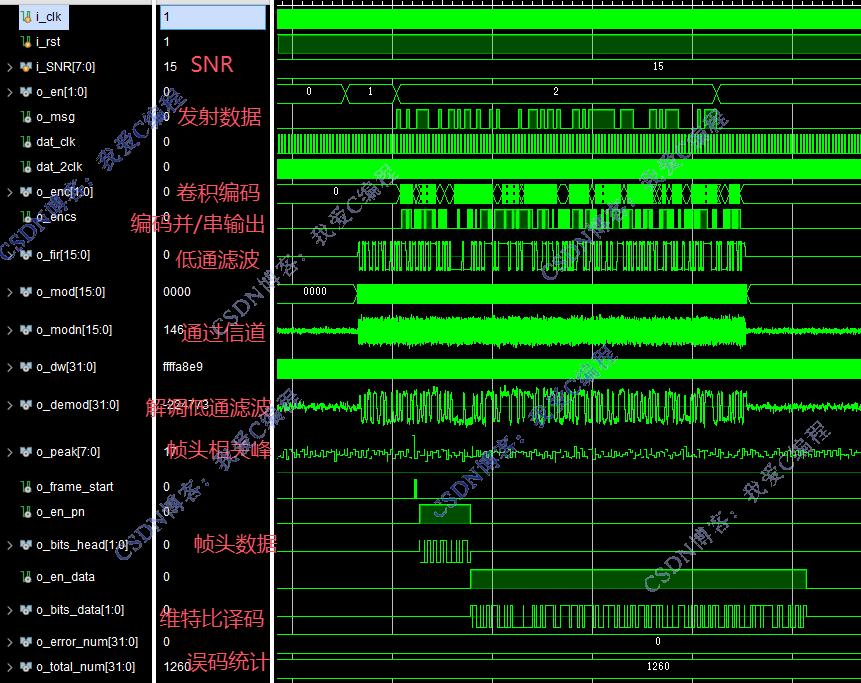

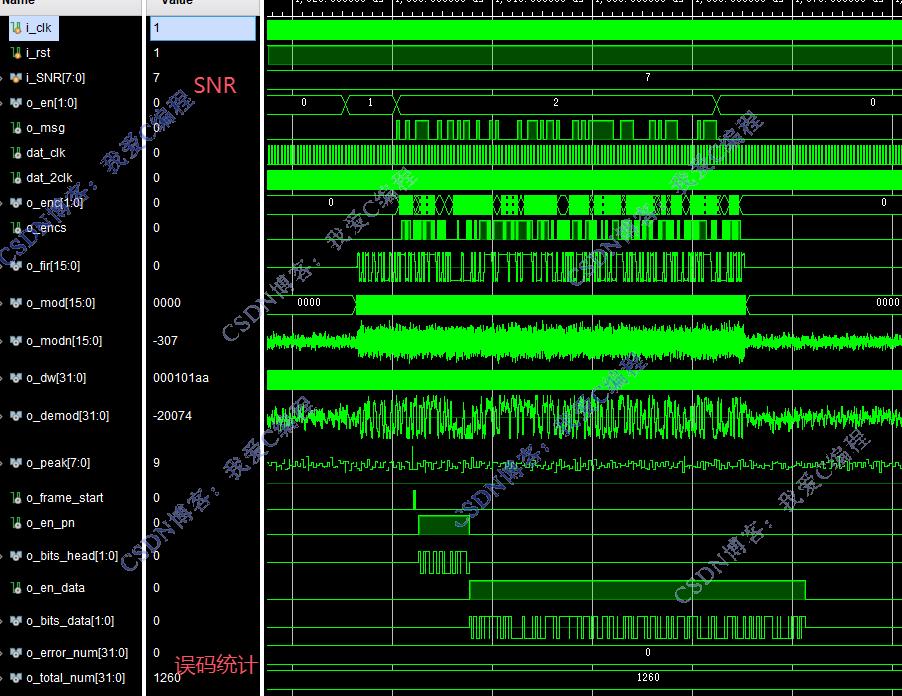

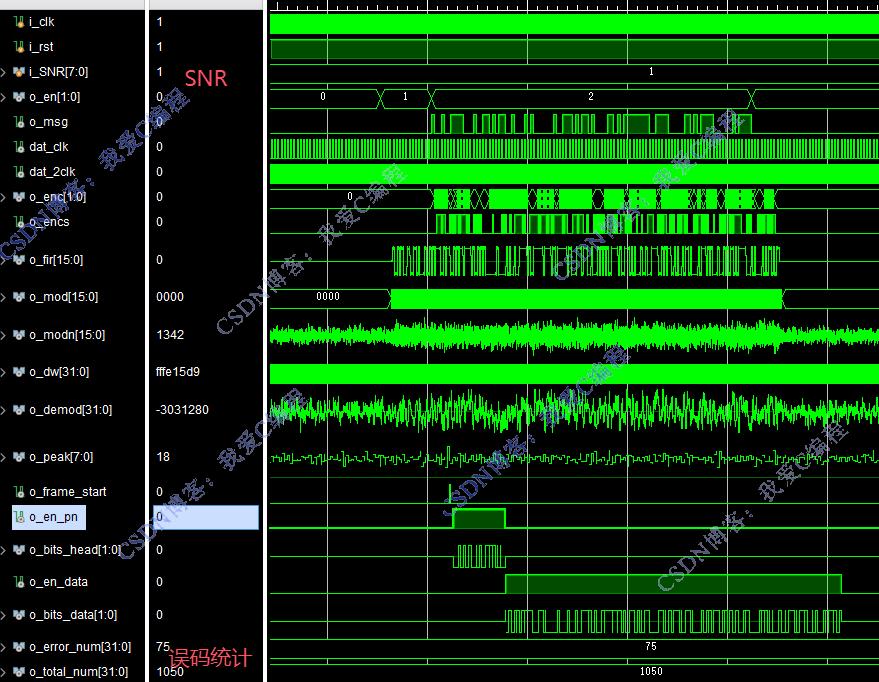

3.部分仿真截图

4.内容简介

基于二进制相移键控(BPSK)、卷积编码及 Viterbi 译码的通信系统,是数字通信领域中典型的抗噪声传输方案。该系统通过卷积编码引入冗余度以抵抗信道干扰,利用Viterbi 算法实现译码,结合BPSK 调制提升频带利用率,并通过帧同步技术确保收发端数据对齐。其核心流程包括:信源→卷积编码→帧同步头插入→BPSK 调制→信道传输→BPSK解调→帧同步→Viterbi 译码。