1.软件版本

vivado2019.2

2.运行方法

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。

3.内容简介

DA算法的主要特点是,巧妙地利用查找表将固定系数的MAC运算转化为查表操作,其运算速度不随系数和输入数据位数的增加而降低,而且相对直接实现乘法器而言,在硬件规模上得到了极大的改善。

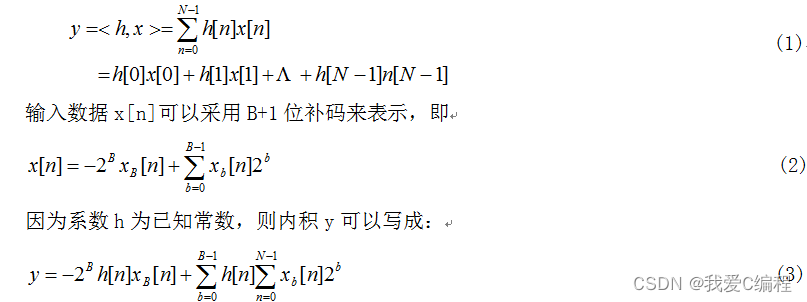

对于FIR(有限长单位冲激响应)滤波器,其基本结构是一个分节的延时线,每一节的输出加权累加,得到滤波器的输出。其输出y就是输入x和系数h的内积:

编辑

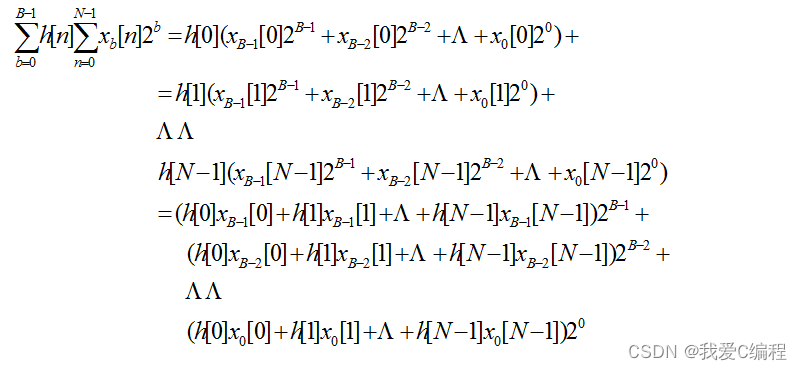

将式(3)中的第二部分展开,重新分别求和,这也是“分布式算法”名称的由来,可以得到:

编辑

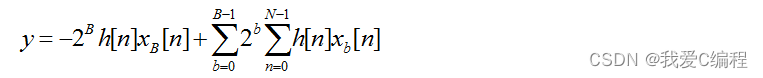

这样就可以将式(3)化简为

编辑

计算h[n]xb[n],就是用查找表实现一个映射,然后再将此映射经过相应的二次幂加权,最后即可得到滤波器的输出。

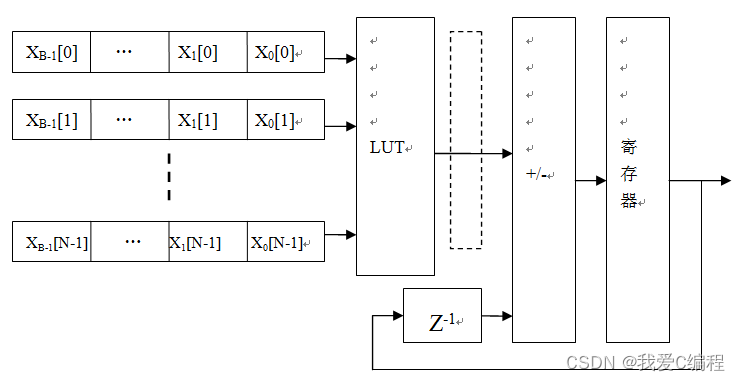

分布式FIR的实现结构

图1给出了分布式FIR滤波器最直接的实现结构,虚线为流水线寄存器。对于小位宽的数据来讲,Da算法不仅速度快,而且所占用的芯片资源也很少。

编辑

图1 移位加法DA结构

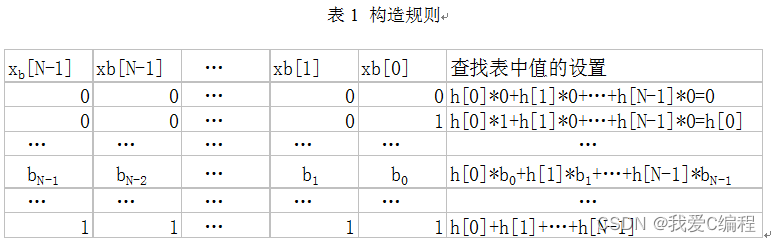

对于式(4)括号中的每一个乘积项都代表了输入变量的某一位与常量的二进制“与”操作,加号代表了算术和操作,指数因子对括号中的值加权。如果事先构造一个查找表,该表储存了括号中所有可能的组合值,就可以通过所有输入变量相对应的组合向量(xb[N-1], xb[N-2], … ,xb[0])对该表进行寻址。该表结构如表1所示。

编辑

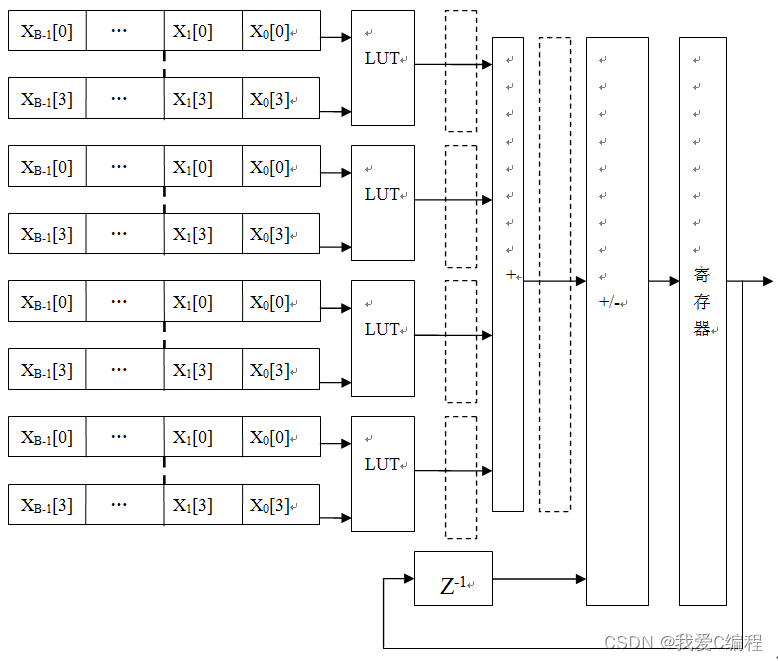

在LUT实现分布式算法是,由于LUT的规模随着N的增加而呈指数增加,如果滤波器系数N过多,则查表的规模十分庞大。为了减小规模,可以利用部分表计算。由于FIR滤波器是线性滤波器,因此低阶滤波器输出可以相加,由此定义一个高阶滤波器的输出。例如,可以把16输入的查找表分割成4个并行的查找表,如图2所示。依次类推,可以将更大的LUT分割成多个小LUT。如果加上流水线,这一结构的改变并不会降低速度,却可以大大减小设计规模。

编辑

图2 简化规模的DA结构

下面开始在FPGA中进行设计与实现。

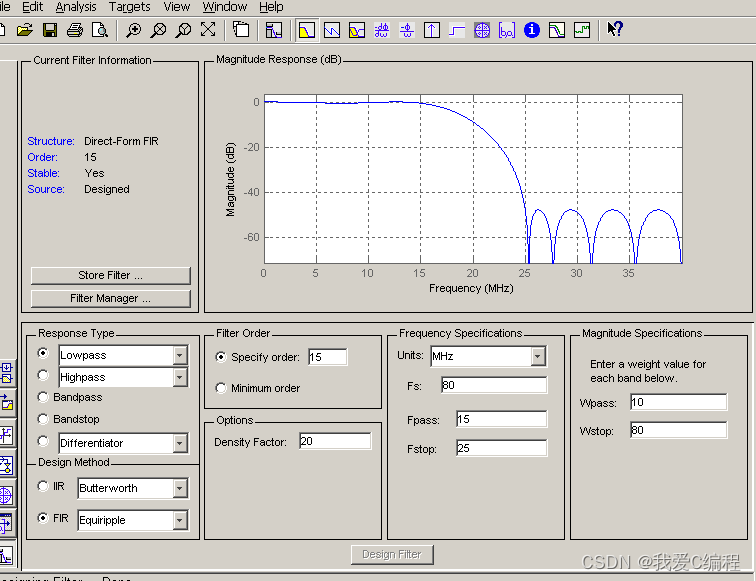

考虑到,基于DA算的程序,其查找表的复杂度会随着输入的位宽和滤波器的阶数的增加而大大增加,这里,我们在满足设计指标的前提下,将滤波器的输入位宽改为12位,阶数为16阶。

4.部分仿真截图

编辑

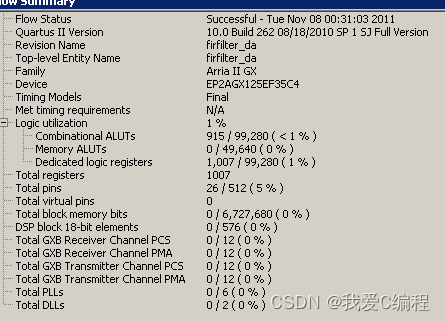

综合结果如下所示:

编辑

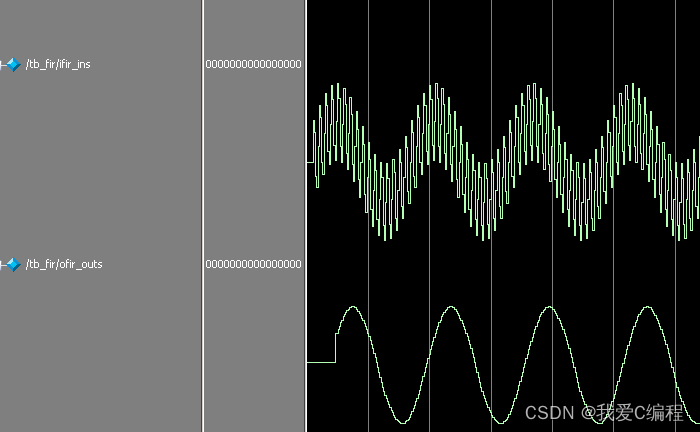

其仿真结果如下所示:

编辑