1.软件版本

vivado2019.2

2.运行方法

使用vivado2019.2或者更高版本打开FPGA工程,然后参考提供的操作录像视频跟着操作。工程路径必须是英文路径。具体操作观看提供的程序操作视频跟着操作。

3.内容简介

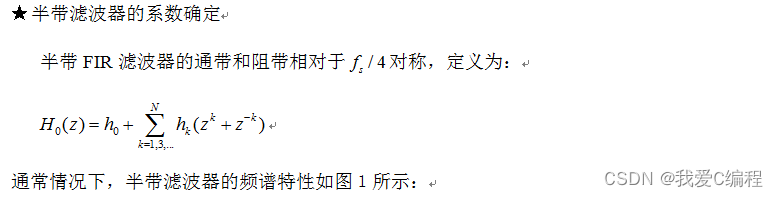

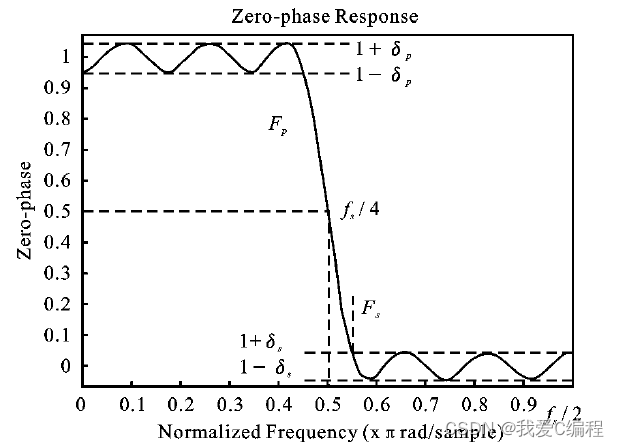

HBF模块由半带滤波器(HBF)和抽取模块组成。该模块的任务是实现2倍抽取进一步降低信号采样速率。由于HBF的冲激响应h(k)除零点外其余偶数点均为零,所以用HBF实现2倍抽取可以节省一半的运算量,对增强软件无线电的实时性非常重要,HBF还具有参数约束少,设计容易、方便的特点。半带滤波器的主要作用是滤除信号高频部分,防止抽取过程后信号发生频谱混叠。

在实际中,需要将输入信号进行多次滤波和抽取,并逐次降低采样率,同时也降低对每一级抗混叠滤波器的要求,所以需要使用半带滤波器进行设计与实现。

阻带衰减: ≥50dB

通带不平坦度:≤2dB

通常情况下,半带滤波器的有三种基本的结构,一般结构,转置结构以及复用结构,下面我们将针对这三种结构的滤波效果以及硬件占用情况进行分析,从而选用最佳的设计方案。

编辑

编辑

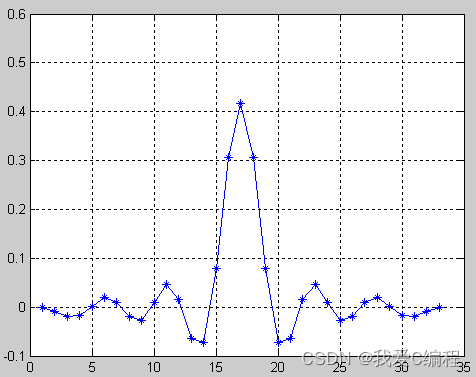

频谱对称性的特点使得半带滤波器的时域冲击响应除极值点以外,在其余所有偶数点都为零,利用该性质,可以将运算量降低一半。

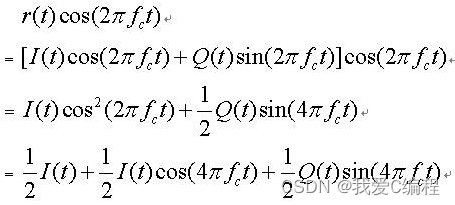

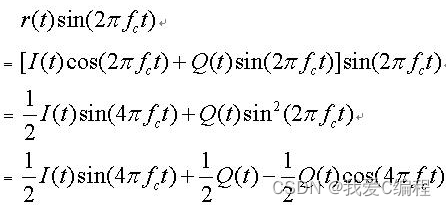

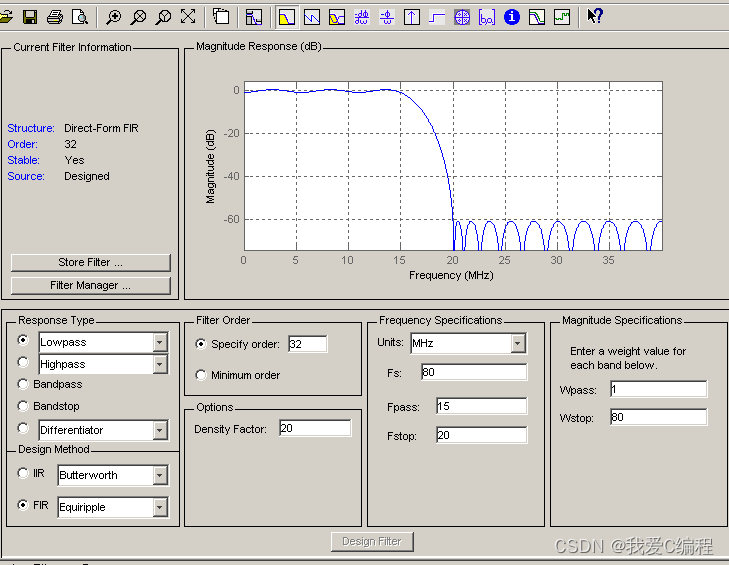

本系统,我们将设计的滤波器,首先,我们可以使用和FIR滤波器设计方法相同的方法进行设计。 根据的设计要求,输入的信号带宽为20M,前面设计的NCO,其载波频率为20M,所以,在进行下变频的时候,会产生两倍的频率分量,具体如下所示:

编辑

= = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = =

编辑

所以,需要设计一个滤波器,其截止频率可以设定为20M,即大于20M的全部滤除,所以,通过上式,可以将其中的高频分量滤除掉。

此外,由于你的要求中提高通带通带不平坦度≤2dB,那么通常情况下,滤波器的阶数需要设计为中高阶,这里,我们选用65阶的滤波器。

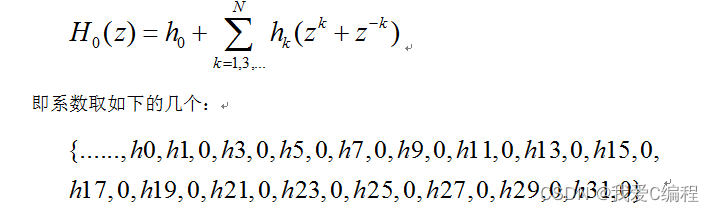

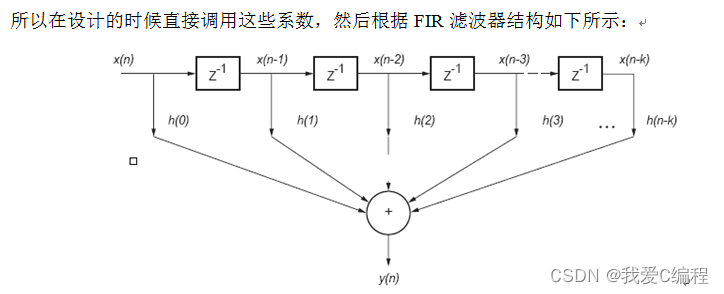

普通滤波器的结构,就是一般的FIR滤波器的结构,只是系数取一般,进行半带滤波,根据半带滤波的表达式,

编辑

编辑 这个结构式最传统的FIR滤波器的结构,我们首先来进行最简单的结构设计。

然后根据半带滤波器的性质,这里我们只需要做如下的运行进行就可以了。

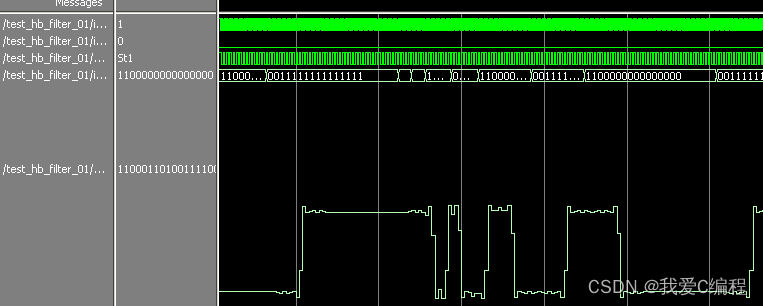

4.部分仿真截图

编辑

编辑

编辑